#### **Faculty of Computers and Artificial Intelligence**

# **CS222: Computer Architecture**

### **Assignment no 02:**

## **Chapter 2: Combinational Logic Design**

Note: You can check the exercises after the Chapter of the Book. In our assignment, we are using  $2^{nd}$  Edition of "Digital Design and Computer Architecture" By David harris and Sarah harris.

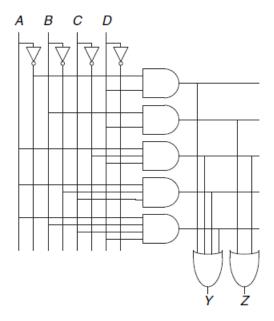

**Exercise 2.24** Write Boolean equations for the circuit in Figure 2.82. You need not minimize the equations.

Figure 2.82 Circuit schematic

-----

**Exercise 2.34** Complete the design of the seven-segment decoder segments  $S_c$  through  $S_g$  (see Example 2.10):

- (a) Derive Boolean equations for the outputs  $S_c$  through  $S_g$  assuming that inputs greater than 9 must produce blank (0) outputs.

- (b) Derive Boolean equations for the outputs  $S_c$  through  $S_g$  assuming that inputs greater than 9 are don't cares.

- (c) Sketch a reasonably simple gate-level implementation of part (b). Multiple outputs can share gates where appropriate.

### **Faculty of Computers and Artificial Intelligence**

# **CS222: Computer Architecture**

**Exercise 2.36** A priority encoder has  $2^N$  inputs. It produces an N-bit binary output indicating the most significant bit of the input that is TRUE, or 0 if none of the inputs are TRUE. It also produces an output NONE that is TRUE if none of the inputs are TRUE. Design an eight-input priority encoder with inputs  $A_{7:0}$  and outputs  $Y_{2.0}$  and NONE. For example, if the input is 00100000, the output Y should be 101 and NONE should be 0. Give a simplified Boolean equation for each output, and sketch a schematic.